吕熠娜,博士,硕士生导师,现为厦门大学信息学院计算机科学与技术系助理教授。2023年获得华东师范大学工学博士学位。曾担任香港城市大学博士后。2024年11月加入厦门大学信息学院。

教学方面:

担任2024年-2025年春季学期国际化课程《人工智能:机器学习在决策、网络安全与计算机集群中的应用》课程助教。承担《计算机组成原理》课程建设与教学方案改革。2025年-2026年秋季学期起,主讲课程《计算机组成原理》。秉承“以学生为中心”的理念,注重启发思维、夯实基础,同时融合行业前沿动态,致力于培养兼具扎实功底与创新能力的计算机人才。

科研方面:

目前主要从事存储系统、存储介质、键值存储系统等研究方向。致力于提升高密度闪存存储介质的可靠性和使用寿命;优化键值存储系统的IO性能等。在闪存存储系统领域已发表学术论文20余篇,累计被引用次数200余次。包括IEEE TCAD, ACM TACO, HPCA, ASPLOS, DAC, DATE, ICCD, ASP-DAC, HotStorage, GLSVLSI, NAS等国际学术会议和期刊。授权发明专利3项。荣获CCF信息存储技术专业委员会优秀博士激励计划入选者(2024)、阿里云-CCF存储专委联合颁发的优秀论文奖(2020)等。担任CCF信息存储技术专业委员会执行委员。

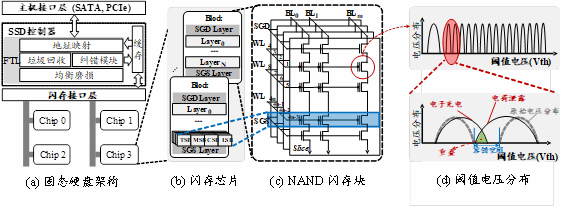

图1 以闪存为介质的固态硬盘架构

代表性成果:

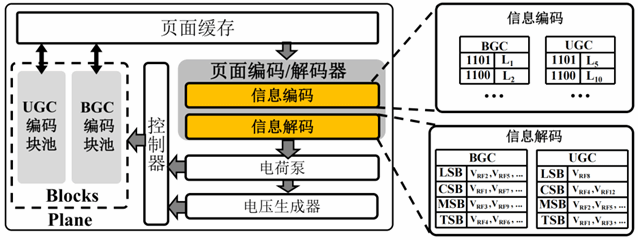

(1)基于多格雷码的高密度闪存数据编码技术

针对高密度闪存数据编码和两步编程算法,考虑到目前芯片生产厂商支持固定的两步编程算法和单一的格雷编码,无法动态适配复杂多变的负载特征和底层介质的可靠性变化特征,提出了一种基于多格雷码的高密度闪存数据编码技术,解决了固定格雷码编码带来的性能瓶颈。

图2 格雷码仲裁方法

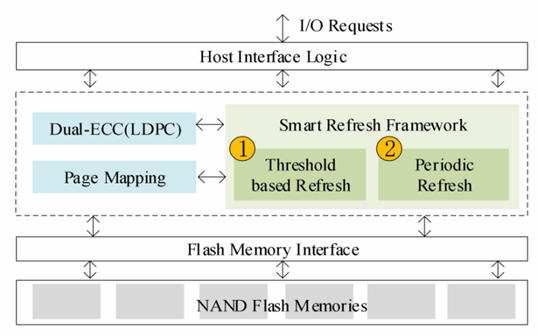

(2)基于LDPC纠错感知的高密度闪存刷新技术

针对高密度闪存中数据错误率高的问题,解决LDPC纠错码在低可靠性闪存设备上引入的长尾延迟问题。观察到基于LDPC的闪存在低可靠性下会出现严重的尾端延迟,并展开基于LDPC 纠错感知的高密度闪存刷新技术研究。提出了一套闪存智能刷新方法,包括阈值刷新机制和巡检刷新机制,有效降低尾端延迟。

图3智能刷新的SSD架构图